Windows operating system misconfiguration is the main cause of Link State Power Management error codes

Therefore, we strongly suggest using the downloadable Link State Power Management Repair Kit to fix Link State Power Management errors

The following discussion features detailed instructions for fixing Link State Power Management errors in Windows system files. Both manual and automated techniques are described that are designed for novice and advanced users, respectively. The overview also provides basic troubleshooting procedures to follow in order to resolve typical causes of Link State Power Management error codes.

What are Link State Power Management errors?

A Link State Power Management error code is caused by a Hexadecimal formatting error. That format is the most common one that software programmers employ for Windows system files and Windows OS-compatible hardware drivers and software apps.

Manufacturers and developers of software apps and hardware drivers use different codes to indicate various types of errors. The Link State Power Management error message appears as a long numerical code along with a technical description of its cause. In many instances, a Link State Power Management error code could have multiple Link State Power Management parameters. Each hexadecimal code denotes a different memory address location that loaded instructions when the error was generated.

Additional messages associated with this matter:

- Install Link State Power Management

- Reinstall Link State Power Management

- Link State Power Management crash

- Link State Power Management is missing

- Remove Link State Power Management

- Download Link State Power Management

- Link State Power Management virus

How are Link State Power Management error codes caused?

Most Link State Power Management errors are due to damaged files in a Windows operating system. Windows system file entry corruption is a serious matter, as it often means a malfunction that may pose a major security risk. If left unchecked, it could result in total and permanent loss of all data and inoperability of the storage media and/or PC device. Jonas brothers sucker mp3 free download deluxe.

Numerous events may trigger system file errors. Most common examples include: 1) incomplete software installation; 2) incomplete software uninstallation; 3) improperly deleted hardware drivers, and 4) improperly deleted software applications. Also, Link State Power Management errors are very common during PC restarts that immediately follow a previous improper shutdown and recent virus or malware infection recovery. Such incidents often result in the corruption or even total deletion of essential Windows system files. When system files are missing or corrupted, data that is essential to run software applications properly cannot be linked correctly.

Specific causes and solutions for Link State Power Management errors

- Reboot your PC. Insufficient memory errors are often resolved by merely rebooting the device. Try that simple task first to see if it fixes the error code problem.

- Insufficient RAM. Verify that your system has enough RAM to run various software applications. System requirements are typically included inside the package that the program CDs came in or listed on the software manufacturer's website under 'Documentation' or a similar heading.

- Memory mismanagement. Many applications require installation of memory management programs. If your system already has a memory management application, uninstall it to see if that resolves the problem.

- Insufficient disk space: Before installing any new software or driver, verify free space availability of at least 100 to 500 megabytes on your PC's hard drive. Any amount below that might prevent the swap file from expanding when required, due to inadequate free space.

To check HD free space on Windows 95, 98, NT, 2000, ME, XP, Vista, and 7, open 'My Computer' or 'Computer.' Then, place your mouse cursor over the desired and right click. Next, left click 'Properties' on the pop-up menu. A dialog will open that displays the amount of free space and total storage capacity. - Software program problems. If recurrent memory-related Link State Power Management errors occur when specific programs are executed, the software itself is likely at fault. Conduct a search and install any update or patches. If errors continue or no update(s) or patch(es) are available, contact the software designer or distributor for assistance.

- System memory defects. If all the above-listed steps fail to resolve memory-related Link State Power Management error codes, your PC's memory may be the culprit. Defective or deteriorating memory can result in software memory errors and even cause the whole system to crash.

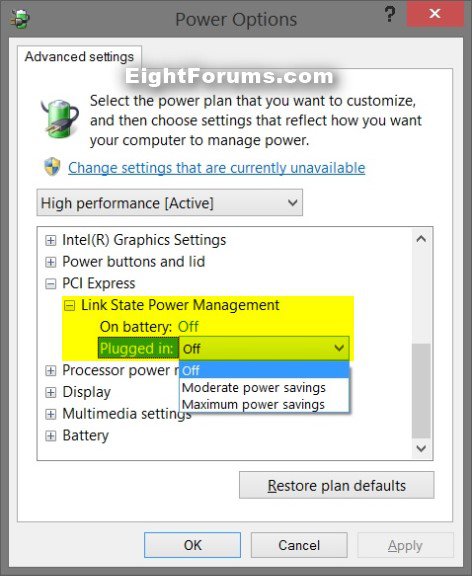

Windows Power Management

Below are instructions to detect bad memory. First, temporarily remove any newly installed memory sticks from the RAM sink. Then, restart your system and see if programs run properly on just the older memory modules.

Specialized programs are also available to diagnose system memory issues. Both Windows Vista and Windows 7 systems have a pre-installed Memory Diagnostics tool. To activate it, click the 'Start' button and enter 'memory' in the 'Run' field. You will be prompted to select immediate restart or next restart to execute the memory test.

Easiest way to fix Link State Power Management errors

Two methods for fixing Link State Power Management errors:

Manual Method for Advanced Users

- Boot up your system and login as Administrator

- Click 'Start,' then 'All Programs' > 'Accessories' > 'System Tools' > 'System Restore.'

- Inside the dialog box that opens, select 'Restore computer to an earlier date' and click 'Next.'

- Select the system restore point with the latest date from 'On this list, click a restore point.'

- Click 'Next'

- Click 'Next' again on the confirmation dialog box that opens.

- Automatic System Restore will begin and restart the device once it completes.

Automatic Solution for Novice PC Users (no manual option selections are required):

- Download the Link State Power Management Repair Tool

- Install the application after download completes

- Click the 'Scan' button that appears on the first interface

- Click the 'Fix Errors' icon that will appear once the automatic scan has finished

- Restart your system as usual

Was this information useful? Yes

Applies to:

Microsoft Windows Update

Microsoft Update

Vista Business

Vista Enterprise

Vista Home Basic

Vista Home Premium

Windows Vista Starter

Vista Ultimate

Windows 7 Enterprise

Windows 7 Home Basic

Windows 7 Home Premium

Windows 7 Professional

Windows 7 Starter

Windows 7 Ultimate

Windows 8

Windows 8 Enterprise

Windows 8 Professional

Microsoft Update

Vista Business

Vista Enterprise

Vista Home Basic

Vista Home Premium

Windows Vista Starter

Vista Ultimate

Windows 7 Enterprise

Windows 7 Home Basic

Windows 7 Home Premium

Windows 7 Professional

Windows 7 Starter

Windows 7 Ultimate

Windows 8

Windows 8 Enterprise

Windows 8 Professional

PCI Express defines Link power management states, replacing the bus power management states that were defined by the PCI Bus Power Management Interface Specification. Link states are not visible to PCI-PM legacy compatible software, and are either derived from the power management D-states of the corresponding components connected to that Link or by ASPM protocols (see Section 5.4.1).

Note that the PCI Express Physical Layer may define additional intermediate states. Refer to Chapter 4 for more detail on each state and how the Physical Layer handles transitions between states.

PCI Express-PM defines the following Link power management states:

- L0 – Active state.

- L0 support is required for both ASPM and PCI-PM compatible power management.

- All PCI Express transactions and other operations are enabled.

- L0s – A low resume latency, energy saving “standby” state.

- L0s support is optional for ASPM unless the applicable form factor specification for the Link explicitly requires L0s support. It is not applicable to M-PCIe implementations. It is not applicable to PCI-PM compatible power management.

- All main power supplies, component reference clocks, and components’ internal PLLs must be active at all times during L0s. TLP and DLLP transmission is disabled for a Port whose Link is in Tx_L0s.

- The Physical Layer provides mechanisms for quick transitions from this state to the L0 state. When common (distributed) reference clocks are used on both sides of a Link, the transition time from L0s to L0 is typically less than 100 Symbol Times.

- It is possible for the Transmit side of one component on a Link to be in L0s while the Transmit side of the other component on the Link is in L0.

- L1 – Higher latency, lower power “standby” state.

- L1 PM Substates functionality is not applicable and must not be enabled for M-PCIe Ports.

- L1 support is required for PCI-PM compatible power management. L1 is optional for ASPM unless specifically required by a particular form factor.

- When L1 PM Substates is enabled by setting one or more of the enable bits in the L1 PM Substates Control 1 Register this state is referred to as the L1.0 substate.

- All main power supplies must remain active during L1. As long as they adhere to the advertised L1 exit latencies, implementations are explicitly permitted to reduce power by applying techniques such as, but not limited to, periodic rather than continuous checking for Electrical Idle exit, checking for Electrical Idle exit on only one Lane, and powering off of unneeded circuits. All platform-provided component reference clocks must remain active during L1, except as permitted by Clock Power Management (using CLKREQ#) and/or L1 PM Substates when enabled. A component’s internal PLLs may be shut off during L1, enabling greater power savings at a cost of increased exit latency.1

- The L1 state is entered whenever all Functions of a Downstream component on a given Link are programmed to a D-state other than D0. The L1 state also is entered if the Downstream component requests L1 entry (ASPM) and receives positive acknowledgement for the request.

- Exit from L1 is initiated by an Upstream-initiated transaction targeting a Downstream component, or by the Downstream component’s initiation of a transaction heading Upstream. Transition from L1 to L0 is typically a few microseconds.

TLP and DLLP transmission is disabled for a Link in L1. - L1 PM Substates – optional L1.1 and L1.2 substates of the L1 low power Link state for PCIPM and ASPM.

- In the L1.1 substate, the Link common mode voltages are maintained. The L1.1 substate is entered when the Link is in the L1.0 substate and conditions for entry into L1.1 substate are met. See Section 5.5.1 for details.

- In the L1.2 substate, the Link common mode voltages are not required to be maintained. The L1.2 substate is entered when the Link is in the L1.0 substate and conditions for entry into L1.2 substate are met. See Section 5.5.1. for details.

- Exit from all L1 PM Substates is initiated when the CLKREQ# signal is asserted (see Sections 5.5.2.1 and 5.5.3.3).

- L2/L3 Ready – Staging point for L2 or L3.

- L2/L3 Ready transition protocol support is required.

- L2/L3 Ready is a pseudo-state (corresponding to the LTSSM L2 state) that a given Link enters when preparing for the removal of power and clocks from the Downstream component or from both attached components. This process is initiated after PM software transitions a device into a D3 state, and subsequently calls power management software to initiate the removal of power and clocks. After the Link enters the L2/L3 Ready state the component(s) are ready for power removal. After main power has been removed, the Link will either transition to L2 if Vaux is provided and used, or it will transition to L3 if no Vaux is provided or used. Note that these are PM pseudo-states for the Link; under these conditions, the LTSSM will in, general, operate only on main power, and so will power off with main power removal.

- The L2/L3 Ready state entry transition process must begin as soon as possible following the acknowledgment of a PME_Turn_Off Message, (i.e., the injection of a PME_TO_Ack TLP). The Downstream component initiates L2/L3 Ready entry by sending a PM_Enter_L23 DLLP. Refer to Section 5.7 for further detail on power management system Messages.

- TLP and DLLP transmission is disabled for a Link in L2/L3 Ready.

- Note: Exit from L2/L3 Ready back to L0 will be through intermediate LTSSM states. Refer to Chapter 4 for detailed information.

- L2 – Auxiliary-powered Link, deep-energy-saving state.

- L2 support is optional, and dependent upon the presence of Vaux.

- A component may only consume Vaux power if enabled to do so as described in Section 5.6.1.

- In L2, the component’s main power supply inputs and reference clock inputs are shut off.

- When in L2, any Link reactivation wakeup logic (Beacon or WAKE#), PME context, and any other “keep alive” logic is powered by Vaux.

- TLP and DLLP transmission is disabled for a Link in L2.

- L3 – Link Off state.

- When no power is present, the component is in the L3 state.

- LDn – A transitional Link Down pseudo-state prior to L0.

- This pseudo-state is associated with the LTSSM states Detect, Polling, and Configuration, and, when applicable, Disabled, Loopback, and Hot Reset.

Refer to Section 4.2 for further detail relating to entering and exiting each of the L-states between L0 and L2/L3 Ready (L2.Idle from the Chapter 4 perspective). The L2 state is an abstraction for PM purposes distinguished by the presence of auxiliary power, and should not be construed to imply a requirement that the LTSSM remain active.

The electrical section specifies the electrical properties of drivers and Receivers when no power is applied. This is the L3 state but the electrical section does not refer to L3.

Figure 5-1 highlights the legitimate L-state transitions that may occur during the course of Link operation.

Figure 5-1: Link Power Management State Flow Diagram

The L1 and L2/L3 Ready entry negotiations happen while in the L0 state. L1 and L2/L3 Ready are entered only after the negotiation completes. Link Power Management remains in L0 until the negotiation process is completed, unless LDn occurs. Note that these states and state transitions do not correspond directly to the actions of the Physical Layer LTSSM. For example in Figure 5-1, L0 encompasses the LTSSM L0, Recovery, and, during LinkUp, Configuration states. Also, the LTSSM is typically powered by main power (not Vaux), so LTSSM will not be powered in either the L2 or the L3 state.

The following example sequence illustrates the multi-step Link state transition process leading up to entering a system sleep state:

- System software directs all Functions of a Downstream component to D3hot.

- The Downstream component then initiates the transition of the Link to L1 as required.

- System software then causes the Root Complex to broadcast the PME_Turn_Off Message in preparation for removing the main power source.

- This Message causes the subject Link to transition back to L0 in order to send it and to enable the Downstream component to respond with PME_TO_Ack.

- After sending the PME_TO_Ack, the Downstream component initiates the L2/L3 Ready transition protocol.

L0 → L1 → L0 → L2/L3 Ready

As the following example illustrates, it is also possible to remove power without first placing all Functions into D3hot:

- System software causes the Root Complex to broadcast the PME_Turn_Off Message in preparation for removing the main power source.

- The Downstream components respond with PME_TO_Ack.

- After sending the PME_TO_Ack, the Downstream component initiates the L2/L3 Ready transition protocol.

L0 → L2/L3 Ready

The L1 entry negotiation (whether invoked via PCI-PM or ASPM mechanisms) and the L2/L3 Ready entry negotiation map to a state machine which corresponds to the actions described later in this chapter. This state machine is reset to an idle state. For a Downstream component, the first action taken by the state machine, after leaving the idle state, is to start sending the appropriate entry DLLPs depending on the type of negotiation. If the negotiation is interrupted, for example by a trip through Recovery, the state machine in both components is reset back to the idle state. The Upstream component must always go to the idle state, and wait to receive entry DLLPs. The Downstream componentmust always go to the idle state and must always proceed to sending entry DLLPs to restart the negotiation.

Table 5-1 summarizes each L-state, describing when they are used, and the platform and component behaviors that correspond to each.

A “Yes” entry indicates that support is required (unless otherwise noted). “On” and “Off” entries indicate the required clocking and power delivery. “On/Off” indicates an optional design choice.

Table 5-1: Summary of PCI Express Link Power Management States

Notes:

- L0s exit latency will be greatest in Link configurations with independent reference clock inputs for components connected to opposite ends of a given Link (vs. a common, distributed reference clock).

- L1 exit latency will be greatest for components that internally shut off their PLLs during this state.

- L2/L3 Ready entry sequence is initiated at the completion of the PME_Turn_Off/PME_TO_Ack protocol handshake. It is not directly affiliated with either a D-State transition or a transition in accordance with ASPM policies and procedures.

- Depending upon the platform implementation, the system’s sleep state may use the L2 state, transition to fully off (L3), or it may leave Links in the L2/L3 Ready state. L2/L3 Ready state transition protocol is initiated by the Downstream component following reception and TLP acknowledgement of the PME_Turn_Off TLP Message. While platform support for an L2 sleep state configuration is optional (depending on the availability of Vaux), component protocol support for transitioning the Link to the L2/L3 Ready state is required.

- L2 is distinguished from the L3 state only by the presence and use of Vaux. After the completion of the L2/L3 Ready state transition protocol and before main power has been removed, the Link has indicated its readiness for main power removal.

- Low-power mobile or handheld devices may reduce power by clock gating the reference clock(s) via the “clock request” (CLKREQ#) mechanism. As a result, components targeting these devices should be tolerant of the additional delays required to re-energize the reference clock during the low-power state exit.

- For example, disabling the internal PLL may be something that is desirable when in D3hot, but not so when in D1 orD2. [본문으로]

'PCI Express' 카테고리의 다른 글

| 5.2. Link State Power Management(0) | 2016.11.02 |

|---|

Active-state power management (ASPM) is a power management mechanism for PCI Express devices to garner power savings while otherwise in a fully active state. Predominantly, this is achieved through active-state link power management; i.e., the PCI Express serial link is powered down when there is no traffic across it. It is normally used on laptops and other mobile Internet devices to extend battery life.

As serial-based PCIe bus devices, such as IEEE1394 (FireWire), become less active, it is possible for the computer's power management system to take the opportunity to reduce overall power consumption by placing the link PHY into a low-power mode and instructing other devices on the link to follow suit. This is usually managed by the operating system's power management software or through the BIOS, thus different settings can be configured for laptop battery mode versus running from the battery charger. Low power mode is often achieved by reducing or even stopping the serial bus clock as well as possibly powering down the PHY device itself.

While ASPM brings a reduction in power consumption, it can also result in increased latency as the serial bus needs to be 'woken up' from low-power mode, possibly reconfigured and the host-to-device link re-established. This is known as ASPM exit latency and takes up valuable time which can be annoying to the end user if it is too obvious when it occurs. This may be acceptable for mobile computing, however, when battery life is critical.

Currently, two low power modes are specified by the PCIe 2.0 specification; L0s and L1 mode. The first mode (L0s) concerns setting low power mode for one direction of the serial link only, usually downstream of the PHY controller. The second mode (L1) is bidirectional and results in greater power reductions though with the penalty of greater exit latency.

See also[edit]

External links[edit]

- 'PCI Express Specifications'. PCI-SIG.

- 'ASPM Optionality (affecting PCIe Base Specification Revision 2.1)'(PDF). PCI-SIG. 2009-06-19. Retrieved 2016-07-16.

Retrieved from 'https://en.wikipedia.org/w/index.php?title=Active_State_Power_Management&oldid=881335964'

Aggressive Link Power Management (ALPM) is a power management protocol for Advanced Host Controller Interface-compliant (AHCI) Serial ATA (SATA) devices, such as hard disk drives and solid-state drives.[1]

Description[edit]

When enabled via the AHCI controller, this allows the SATA host bus adapter to enter a low-power state during periods of inactivity, thus saving energy. The drawback to this is increased periodic latency as the drive must be re-activated and brought back on-line before it can be used, and this will often appear as a delay to the end-user.

States[edit]

There are three states:[2]

- Active

- Low Power with two internal states Partial and Slumber. Partial has a maximum return latency of 10 microseconds while slumber has a maximum latency of 10 milliseconds. Hot swapping is disabled.

- Device Sleep with a maximum return latency of 20 milliseconds unless otherwise specified in Identify Data Log

These can be selected by the SATA AHCI driver, usually via a configuration option. Hot swapping is disabled.

See also[edit]

References[edit]

- ^'Serial ATA AHCI: Specification, Rev. 1.3'. Intel. Retrieved 31 October 2012.

- ^'Designing Energy Efficient SATA Devices'(PDF). Intel. Retrieved 31 October 2012.

External links[edit]

- Aggressive Link Power Management - Red Hat

- 'Designing Energy Efficient SATA Devices'(PDF). - Intel

Retrieved from 'https://en.wikipedia.org/w/index.php?title=Aggressive_Link_Power_Management&oldid=881835366'